本帖最后由 新ちゃん 于 2021-11-27 23:53 编辑

RISC-V之乘除法指令

指令格式

RV32M 具有有符号和无符号整数的除法指令:divide(div)和 divide unsigned(divu),它们将 商放入目标寄存器。在少数情况下,程序员需要余数而不是商,因此 RV32M 提供 remainder(rem)和 remainder unsigned(remu),它们在目标寄存器写入余数,而不是商。 为了正确地得到一个有符号或无符号的 64 位积,RISC-V 中带有四个乘 法指令。要得到整数 32 位乘积(64 位中的低 32 位)就用 mul 指令。要得到高 32 位,如果 操作数都是有符号数,就用 mulh 指令;如果操作数都是无符号数,就用 mulhu 指令;如 果一个有符号一个无符号,可以用 mulhsu 指令。在一条指令中完成把 64 位积写入两个 32 位寄存器的操作会使硬件设计变得复杂,所以 RV32M 需要两条乘法指令才能得到一个完整 的 64 位积。

用乘法代替常数除法

对许多微处理器来说,整数除法是相对较慢的操作。如前述,除数为 2 的幂次的无符号 除法可以用右移来代替。事实证明,通过乘以近似倒数再修正积的高 32 位的方法,可以优 化除数为其它数的除法。例如,图 4.3 显示了 3 为除数的无符号除法的代码。 - 先把数装到t0里面

- addi是立即数与寄存器的数相加, t0-1365放回t0

- a0和t0相乘(无符号)

- 立即数→移,也就是a1右移1位

也就是说从数值上来讲,可以通过乘法代替常数除法。

RISC-V之RV64

尽管 RV64I 有 64 位地址且默认数据大小为 64 位,32 位字仍然是程序中的有效数据类 型。因此,RV64I 需要支持字,就像 RV32I 需要支持字节和半字一样。更具体地说,由于寄 存器现在是 64 位宽,RV64I 添加字版本的加法和减法指令:addw,addiw,subw。这些指 令将计算结果截断为 32 位,结果符号扩展后再写入目标寄存器。 RV64I 也包括字版本的移 位指令(sllw,slliw,srlw,srliw,sraw,sraiw),以获得 32 位移位结果而不是 64 位移 位结果。要进行 64 位数据传输,RV64 提供了加载和存储双字指令:ld,sd。最后,就像 RV32I 中有无符号版本的加载单字节和加载半字的指令,RV64I 也有一个无符号版本的加载 字:lwu。 出于类似的原因,RV64 需要添加字版本的乘法,除法和取余指令:mulw,divw,divuw, remw,remuw。为了支持对单字及双字的同步操作,RV64A 为其所有的 11 条指令都添加 了双字版本。

由于版本众多,这里只选择有代表性的来了解 RV64F 和 RV64D 添加了整数双字转换指令,并称它们为长整数,以避免与双精度浮点 数据混淆:fcvt.l.s,fcvt.l.d,fcvt.lu.s,fcvt.lu.d,fcvt.s.l,fcvt.s.lu,fcvt.d.l,fcvt.d.lu. 由于整数 x 寄存器现在是 64 位宽,它们现在可以保存双精度浮点数据,因此 RV64D 增加了 两个浮点指令:fmv.x.w 和 fmv.w.x.

这里暂时不讲解压缩指令

RISC-V的特权架构

到目前为止,本书主要关注 RISC-V 对通用计算的支持:我们引入的所有指令都在用 户模式(应用程序的代码在此模式下运行)下可用。本章介绍两种新的权限模式:运行最 可信的代码的机器模式(machine mode),以及为 Linux,FreeBSD 和 Windows 等操作系统 提供支持的监管者模式(supervisor mode)。这两种新模式都比用和模式有着更高的权限, 这也是本章标题的来源。有更多权限的模式通常可以使用权限较低的模式的所用功能,并 且它们还有一些低权限模式下不可用的额外功能,例如处理中断和执行 I/O 的功能。处理 器通常大部分时间都运行在权限最低的模式下,处理中断和异常时会将控制权移交到更高 权限的模式。 嵌入式系统运行时(runtime)和操作系统用这些新模式的功能来响应外部事件,如网 络数据包的到达;支持多任务处理和任务间保护;抽象和虚拟化硬件功能等。鉴于这些主 题的广度,为此而编撰的全面的程序员指南会是另外一本完整的书。但我们的这一章节旨 在强调 RISC-V 这部分功能的亮点。

机器模式

机器模式(缩写为 M 模式,M-mode)是 RISC-V 中 hart(hardware thread,硬件线 程)可以执行的最高权限模式。在 M 模式下运行的 hart 对内存,I/O 和一些对于启动和配 置系统来说必要的底层功能有着完全的使用权。因此它是唯一所有标准 RISC-V 处理器都 必须实现的权限模式。实际上简单的 RISC-V 微控制器仅支持 M 模式。这类系统是本节的 重点。

机器模式最重要的特性是拦截和处理异常(不寻常的运行时事件)的能力。RISC-V 将 异常分为两类。

一类是同步异常,这类异常在指令执行期间产生,如访问了无效的存储器 地址或执行了具有无效操作码的指令时。

另一类是中断,它是与指令流异步的外部事件, 比如鼠标的单击。RISC-V 中实现精确例外:保证异常之前的所有指令都完整地执行了,而 后续的指令都没有开始执行(或等同于没有执行)。

图 10.3 列出了触发标准例外的原因。

在 M 模式运行期间可能发生的同步例外有五种:

⚫ 访问错误异常 当物理内存的地址不支持访问类型时发生(例如尝试写入 ROM)。

⚫ 断点异常 在执行 ebreak 指令,或者地址或数据与调试触发器匹配时发生。 ⚫ 环境调用异常 在执行 ecall 指令时发生。

⚫ 非法指令异常 在译码阶段发现无效操作码时发生。

⚫ 非对齐地址异常 在有效地址不能被访问大小整除时发生,例如地址为 0x12 的 amoadd.w

有三种标准的中断源:软件、时钟和外部来源。软件中断通过向内存映射寄存器中存 数来触发,并通常用于由一个 hart 中断另一个 hart(在其他架构中称为处理器间中断机 制)。当实时计数器 mtime 大于 hart 的时间比较器(一个名为 mtimecmp 的内存映射寄存 器)时,会触发时钟中断。外部中断由平台级中断控制器(大多数外部设备连接到这个中 断控制器)引发。

监管者模式

更复杂的 RISC-V 处理器用和几乎所有通用架构相同的方式处理这些问题:使用基于 页面的虚拟内存。这个功能构成了监管者模式(S 模式)的核心,这是一种可选的权限模 式,旨在支持现代类 Unix 操作系统,如 Linux,FreeBSD 和 Windows。S 模式比 U 模式权 限更高,但比 M 模式低。与 U 模式一样,S 模式下运行的软件不能使用 M 模式的 CSR 和 指令,并且受到 PMP 的限制。本届介绍 S 模式的中断和异常,下一节将详细介绍 S 模式 下的虚拟内存系统。 默认情况下,发生所有异常(不论在什么权限模式下)的时候,控制权都会被移交到 M 模式的异常处理程序。但是 Unix 系统中的大多数例外都应该进行 S 模式下的系统调 用。M 模式的异常处理程序可以将异常重新导向 S 模式,但这些额外的操作会减慢大多数 异常的处理速度。因此,RISC-V 提供了一种异常委托机制。通过该机制可以选择性地将中 断和同步异常交给 S 模式处理,而完全绕过 M 模式。

S 模式提供了一种传统的虚拟内存系统,它将内存划分为固定大小的页来进行地址转 换和对内存内容的保护。启用分页的时候,大多数地址(包括 load 和 store 的有效地址和 PC 中的地址)都是虚拟地址。要访问物理内存,它们必须被转换为真正的物理地址,这通 过遍历一种称为页表的高基数树实现。页表中的叶节点指示虚地址是否已经被映射到了真 正的物理页面,如果是,则指示了哪些权限模式和通过哪种类型的访问可以操作这个页。

扩展指令集目前官方提供的risc-v扩展指令集有如下几个(确定将会实现的) 11.1 “B”标准扩展:位操作 …

11.2 “E”标准扩展:嵌入式 …

11.3 “H”特权态架构扩展:支持管理程序(Hypervisor) …

11.4 “J”标准扩展:动态翻译语言 …

11.5 “L”标准扩展:十进制浮点 …

11.6 “N”标准扩展:用户态中断 …

11.7 “P”标准扩展:封装的单指令多数据(Packed-SIMD)指令 …

11.8 “Q”标准扩展:四精度浮点 … 目前根据已经开源的设计方案,大多专注于B/J/Q/L指令的相关扩展

阿里平头哥文档

AI中涉及的运算操作机器学习

- 矩阵的转置、求逆运算

- 矩阵的切片与扩张

- 矩阵的乘法,点积,内积,外积,元素积

- 矩阵的加法,求和(包括求元素的平方和),L1,L2正则化

- 取指数与对数(逻辑回归,信息熵等)

- 标准化、归一化操作

深度学习

- 线性层:矩阵的外积

- 卷积层:矩阵的内积

- 池化层:求矩阵平均值(求和),或求最大值

- 残差网络,GoogleNet等,矩阵拼接

- 随机梯度下降,keep prob:随机值生成

- 压缩解压缩

- 加密解密(MAC运算等)# 5,6两个点涉及大整数操作以及优化,质数生成

- 张量、矢量、标量的运算

现有的AI指令集或其他底层解决方案TPU解决方案

在TPU中,它使用若干条指令来完成矩阵的乘法运算,其中使用Read_Host_Memory来从主存中读取数据至通用缓存(Unified Buffer)中;使用Read_Weights来将权重读取至矩阵单元中。在进行矩阵运算时,使用MatrixMultiply或Convolve来进行矩阵乘法。最后使用Write_Host_Memory来将数据写回主存中。但是在TPU中,它的矩阵乘法对操作数的尺寸存在限制,在MatrixMultiply或Convolve中,其限制操作数为B256 与256256,若矩阵尺寸大与此值,则不太方便直接使用TPU进行运算;若矩阵尺寸小于此值,则需要先对多余部分填充0后再进行计算。

X86

在X86_64中,其在AVX、AVX2等指令集中提供了VMULPS、VMULPD、VADDPS、VADDPD等一系列SIMD指令,这些指令可以使用一条指令来完成多组数据的运算。在矩阵乘法等应用中,数据之间没有相互依赖性,因此可以使用SIMD指令来提高运算效率。

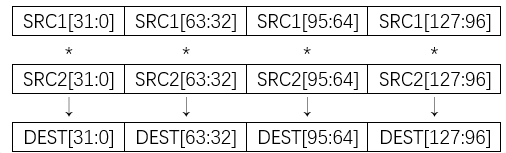

VMULPS指令示意图

与TPU相比,AVX至运算数据的尺寸上没有太多的限制,即使数据的规模较大,也可以拆分为多交指令执行。但这也造成AVX指令集的并行化程度一般不高,通常一条指令只能处理4-8条数据,效率远不如TPU等专门双击的架构,在人工智能的应用上仍然难以满足需要。

现有AI芯片

现有的AI芯片,比如寒武纪的产品为了AI的运算也做了大量适配,比如构建大量的乘法器用来在一个周期内并行处理多个乘法操作,相应地指令集也会向着这个方向进行优化,如华为Ascend 系列AI芯片,内置的都是运算密集型CISC指令集来为AI运算做优化。但是这种设计模式的功耗以及设计的繁琐程度都很高,所以集成AI优化的RISC-V应该在保持灵活小巧的基础上对矩阵运算等AI领域常见的基本数学运算做优化,对机器学习和深度学习有一个泛化支持,虽然速度可能没CISC那么高,但是可以保持其精简以及自由拓展的特点。 |  /2

/2